Le modalità in cui cambiano VDS e ID del MOSFET SiC LS (low-side) sono diversi in caso di accensione e spegnimento. Quando si considera l’effetto di questi cambiamenti sulla tensione gate-source (VGS), il nostro punto di partenza è un circuito equivalente che include i componenti parassiti del circuito di pilotaggio del gate.

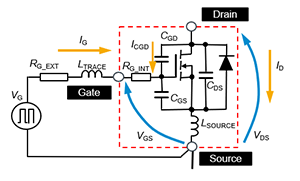

Il diagramma in basso descrive il circuito equivalente del circuito di pilotaggio del gate e del MOSFET SiC su cui si basa l’analisi.

Nel circuito di pilotaggio del gate c’è un segnale di gate (VG), e ci sono anche la resistenza (RG_INT) dovuta alla linea di gate all’interno del SiC MOSFET, così come l’induttanza di sorgente (LSOURCE) del package SiC MOSFET, così come l’induttanza (LTRACE) della traccia del circuito di gate e la resistenza esterna del gate (RG_EXT).

Le polarità delle tensioni e delle correnti sono da considerarsi positive nella direzione indicata dalla corrente di gate (IG) e dalla corrente di drenaggio (ID) nel diagramma del circuito equivalente, e VGS e VDS sono definite con il pin sorgente come riferimento.

La linea di gate all’interno del MOSFET SiC ha anche un’induttanza associata, ma è minore rispetto a LTRACE, e quindi verrà omessa.

Funzionamento di accensione e spegnimento

Per capire il funzionamento di accensione e spegnimento nel circuito a ponte, spiegheremo in dettaglio le forme d’onda di tensione e corrente per ciascuno dei MOSFET SiC nel circuito a ponte mostrato in precedenza.

Quando viene applicata una tensione positiva VG come segnale di gate lato LS per accendere il lato LS, inizia la carica della capacità gate-source (CGS) e VGS sale, e al raggiungimento della tensione di soglia di gate del SiC MOSFET (VGS(th)), l’ID inizia a scorrere sul lato LS, e contemporaneamente l’ID sul lato HS, che scorre dalla sorgente verso il drenaggio, inizia a diminuire. Questo intervallo di tempo viene precedentemente definito come T1 (indicato nella parte inferiore del diagramma della forma d’onda).

Successivamente, quando l’ID lato HS raggiunge il valore zero e il diodo parassita viene spento, la tensione del punto medio (VSW) inizia a scendere, e simultaneamente la capacità di drain-source (CDS) e la capacità drain-gate (CGD) lato HS vengono caricate (T2 nel diagramma della forma d’onda).

Al completamento di questa carica di CDS + CGD sul lato HS (mentre il lato LS viene scaricato), quando la VGS lato LS ha raggiunto una certa tensione, l’operazione di accensione lato LS è completata.

L’operazione di spegnimento inizia con lo spegnimento sul lato LS; la carica accumulata su CGS sul lato LS inizia ad essere scaricata, e quando la tensione di plateau del SiC MOSFET viene raggiunta (quando l’intervallo di effetto specchio è entrato), la VDS lato LS inizia a salire, e contemporaneamente VSW sale.

A questo punto quasi tutta la corrente di carico scorre ancora sul lato LS (T4 nel diagramma della forma d’onda), e una corrente di commutazione non scorre ancora nel diodo parassita lato HS.

Quando la carica dei CDS + CGD lato LS (mentre il lato HS si sta scaricando) è completata, VSW supera la tensione di ingresso (E), il diodo parassita lato HS è acceso, e l’ID lato LS inizia la commutazione verso il lato HS (T5 nel diagramma della forma d’onda).

L’ID lato LS raggiunge finalmente lo zero, entrando in un intervallo di tempo morto (T6 nel diagramma della forma d’onda), e una VG positiva viene applicata come segnale di gate al MOSFET lato HS per accenderlo, costituendo un periodo di funzionamento sincrono (T7 nel diagramma della forma d’onda).

Leggi l’articolo originale e completo su TechWeb